Intel® Arria® 10 FPGA Development Kit

Device 10AX115S2F45I1SG.

The board has 2GB DDR4 memory card with HiLo memory interface.

Arria V board

Device 5AGTFC7H3F35I3.

The board has no external memory. Single-core models were equipped with 512 KB of internal FPGA-based memory. The dual-core model has 256 KB for each core.

Device 5AGTFC7H3F35I3.

The board has no external memory. Single-core models were equipped with 512 KB of internal FPGA-based memory. The dual-core model has 256 KB for each core.

X16 core

Logic utilization (in ALMs) = 46090 / 91680 ( 50% )

Total registers = 40298

Total block memory bits = 6303878 / 13987840 ( 45 % )

Total DSP Blocks = 41 / 800 ( 5 % )

Slow 1150mV 100C Model = 115 MHz

Slow 1150mV -40C Model = 125 MHz

Fast 1150mV 100C Model = 146 MHz

Fast 1150mV -40C Model = 189 MHz

X16E core

Logic utilization (in ALMs) = 58840 / 91680 ( 64% )

Total registers = 46221

Total block memory bits = 6304185 / 13987840 ( 45 % )

Total DSP Blocks = 77 / 800 ( 10 % )

Slow 1150mV 100C Model = 105 MHz

Slow 1150mV -40C Model = 122 MHz

Fast 1150mV 100C Model = 130 MHz

Fast 1150mV -40C Model = 167 MHz

X16T2 core

Logic utilization (in ALMs) = 68571 / 91680 ( 75% )

Total registers = 50572

Total block memory bits = 6714103 / 13987840 ( 48 % )

Total DSP Blocks = 41 / 800 ( 5 % )

Slow 1150mV 100C Model = 100 MHz

Slow 1150mV -40C Model = 113 MHz

Fast 1150mV 100C Model = 123 MHz

Fast 1150mV -40C Model = 158 MHz

X32 core

Logic utilization (in ALMs) = 63417 / 91680 ( 69% )

Total registers = 43861

Total block memory bits = 6817048 / 13987840 ( 49 % )

Total DSP Blocks = 53 / 800 ( 7 % )

Slow 1150mV 100C Model = 94 MHz

Slow 1150mV -40C Model = 106 MHz

Fast 1150mV 100C Model = 117 MHz

Fast 1150mV -40C Model = 152 MHz

X16 with a DualFFT unit

Logic utilization (in ALMs) = 47502 / 91680 ( 52% )

Total registers = 43464

Total block memory bits = 6310662 / 13987840 ( 45 % )

Total DSP Blocks = 45 / 800 ( 6 % )

Slow 1150mV 100C Model = 109 MHz

Slow 1150mV -40C Model = 120 MHz

Fast 1150mV 100C Model = 136 MHz

Fast 1150mV -40C Model = 174 MHz

X16x2 (dual-core)

Logic utilization (in ALMs) = 85560 / 91680 ( 93% )

Total registers = 74726

Total block memory bits = 8379452 / 13987840 ( 60 % )

Total DSP Blocks = 82 / 800 ( 10 % )

Slow 1150mV 100C Model = 102 MHz

Slow 1150mV -40C Model = 116 MHz

Fast 1150mV 100C Model = 126 MHz

Fast 1150mV -40C Model = 161 MHz

Arria II board

Device EP2AGX125EF29I3

1GB DDR2 SDRAM.

Only the X16 core was loaded onto this board. The core was supplemented with a DDR2 400 SDRAM (Altera ALTMEMPHY core) controller,

Logic utilization = 96 %

Dedicated logic registers = 42839 / 99280 ( 43 % )

Total block memory bits = 2759078 / 6727680 ( 41 % )

DSP block 18-bit elements = 92 / 576 ( 16 % )

Slow timing model = 110 MHz

Fast timing model = 205 MHz

Stratix IV GX FPGA Development Board, 530 Edition

X32Carrier core with a graphic accelerator.

Main memory: DDR3 512MByte

Videobuffer memory: 4 MByte

Memory frequency: 300MHz

Core frequency: 150MHz

Resource utilization

Logic utilization: 52 %

Total block memory bits: 4,577,400 / 21,233,664 ( 22 % )

DSP block 18-bit elements: 130 / 1,024 ( 13 % )

Total PLLs: 4 / 8 ( 50 % )

Total DLLs: 2 / 4 ( 50 % )

Two X32Carrier base cores

Main memory: 256KByte per core

Cores frequency: 130MHz

Resource utilization

Logic utilization: 66 %

Total block memory bits: 8,084,640 / 21,233,664 ( 38 % )

DSP block 18-bit elements: 236 / 1,024 ( 23 % )

Total PLLs: 1 / 8 ( 13 % )

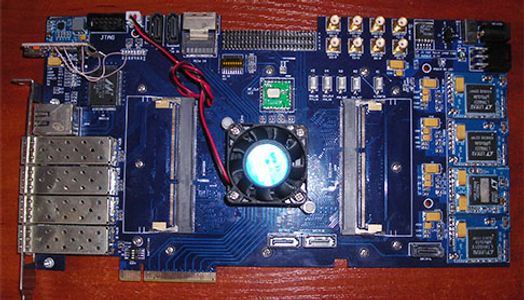

Stratix V DE5-Net board

Device 5SGXEA7N2F45C2

Two banks of DDR3 memory 2 GB in each slot. Four 8Mbyte QDRII chips. Intel IP functions of the DDR3 and QDRII memory controllers with the Avalon interface were used to connect the processor cores to the corresponding types of memory.

X16

QDR Memory

Logic utilization (in ALMs) = 46616 / 234720 ( 20 % )

Total registers = 41342

Total block memory bits = 2084560 / 52428800 ( 4 % )

Total DSP Blocks =41 / 256 ( 16 % )

Slow 900mV 85C Model = 176 MHz

Slow 900mV 0C Model = 188 MHz

Fast 900mV 85C Model = 255 MHz

Fast 900mV 0C Model = 279 MHz

DDR3 Memory

Logic utilization (in ALMs) = 50665 / 234720 ( 22 % )

Total registers = 48634

Total block memory bits = 2944720 / 52428800 ( 6 % )

Total DSP Blocks =41 / 256 ( 16 % )

Slow 900mV 85C Model = 164 MHz

Slow 900mV 0C Model = 174 MHz

Fast 900mV 85C Model = 243 MHz

Fast 900mV 0C Model = 265 MHz

X32

DDR3 Memory

Logic utilization (in ALMs) = 73828 / 234720 ( 31 % )

Total registers = 54828

Total block memory bits = 3483536 / 52428800 ( 7 % )

Total DSP Blocks =49 / 256 ( 19 % )

Slow 900mV 85C Model = 156 MHz

Slow 900mV 0C Model = 166 MHz

Fast 900mV 85C Model = 227 MHz

Fast 900mV 0C Model = 247 MHz

Internal 512KB SSRAM mode

Logic utilization (in ALMs) = 64214 / 234720 ( 27 % )

Total registers = 45337

Total block memory bits = 6817680 / 52428800 ( 13 % )

Total DSP Blocks =49 / 256 ( 19 % )

Slow 900mV 85C Model = 158 MHz

Slow 900mV 0C Model = 170 MHz

Fast 900mV 85C Model = 229 MHz

Fast 900mV 0C Model = 244 MHz

X16x4 (quad-core system)

QDRII Memory 8Mb per core

Logic utilization (in ALMs) = 180244 / 234720 ( 77 % )

Total registers = 157462

Total block memory bits = 12617456 / 52428800 ( 24 % )

Total DSP Blocks =164 / 256 ( 64 % )

Slow 900mV 85C Model = 164 MHz

Slow 900mV 0C Model = 176 MHz

Fast 900mV 85C Model = 238 MHz

Fast 900mV 0C Model = 261 MHz

QuadThread Core two X16 and two X32

DDR3 Memory

Logic utilization (in ALMs) = 206629 / 234720 ( 88 % )

Total registers = 133787

Total block memory bits = 6437980 / 52428800 ( 12 % )

Total DSP Blocks =180 / 256 ( 70 % )

Slow 900mV 85C Model = 150 MHz

Slow 900mV 0C Model = 163 MHz

Fast 900mV 85C Model = 216 MHz

Fast 900mV 0C Model = 234 MHz

Kintex 7 Board

Device XC7K420

Implemented X16 runs at 100 MHz.

Internal SRAM 512 Kb

FPGA resources:

LUT - 62572 / 260600 (24%)

LUTRAM - 5091 / 108600 (4.69%)

FF - 29705 / 521200 (5.70%)

BRAM - 179.5 / 835 (21.5%)

DSP - 46 / 1680 (2.74)

Core X32

System clock 100 MHz.

Internal SRAM 512 Kb

FPGA resources:

LUT - 111498 / 260600 (42.79%)

LUTRAM - 20745 / 108600 (19.1%)

FF - 42852 / 521200 (8.22%)

BRAM - 188 / 835 (22.51%)

DSP - 62 / 1680 (3.69)

Two X32 cores

System clock 100 MHz.

Internal SRAM 512 Kb per core

FPGA resources:

LUT - 222679 / 260600 (85.45%)

LUTRAM - 41522 / 108600 (38.23%)

FF - 87075 / 521200 (16.71%)

BRAM - 376 / 835 (45.03%)

DSP - 124 / 1680 (7.38)